International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 5, Issue 11, November 2016

# Design of 4-Bit Pipeline ADC using Switch Capacitor Circuit in 0.25µm CMOS Technology at 2.5 V

Sumit Jaiswal Megha Soni<sup>1</sup>, Vijay Sharma<sup>2</sup>

(SVCE, INDORE)<sup>1,2</sup>

**Abstract:** A 4-bit pipeline Analog-to-digital Converter (ADC) is designed using switched capacitor circuit. ADC is designed in 3 stages, 1.5 bit/stage pipeline is used in first two stages and third stage uses two bit flash ADC. The ADC is designed on 0.25 µm CMOS technology at 2.5 V supply voltage in Tanner EDA tool. S/H is used in first stages that consume most of the power consumed by the ADC, after first stage S/H circuit is removed, and also the scaling is used to reduce the power consumption. Cascode opamp is designed with gain of 72.52 dB, phase margin of 66° and unity gain bandwidth of 162.61MHz. The ADC is designed at sampling rate of 5 MS/s and consumes 158.1208 mW powers.

**Keywords:** Analog-to-digital conversion (ADC), capacitor sharing, opamp sharing, switched capacitor, pipeline ADC, Non overlapping clock.

# I. INTRODUCTION

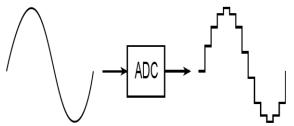

Analog to digital and digital to analog converters are the bridge between the analog world and digital world. Natural signals are analog in nature but better signal processing in digital domain forces to convert analog signal to digital signal. Noise and device limitation limits the bandwidth of analog circuits, also its complex analysis makes design complex. Basic concept of analog to digital converter is shown in the Fig. 1.

Fig.1 Basic concept of an analog to digital converter

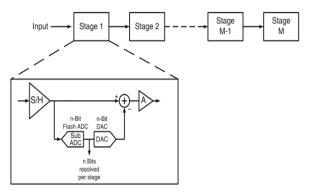

Pipeline ADCs are high speed ADCs capable of resolving medium to high resolutions. [1] These ADCs converts analog signals into digital signals in many stages, each stage converts a portion of input signal to output resolution. The output of first stage is most significant bits (MSB) and the subsequent stages convert LSB bits until the least significant bits (LSB) are converted.

The general architecture of a pipeline ADC is shown in Figure 3.12. Each stage has a similar structure, shown exploded in Figure 3.12. Each block contains a sample and hold block to sample the analog signal. Each stage has its own small flash converter that resolves n-bits. This n-bit output is fed back through a DAC and the converted binary output of sub ADC is subtracted from the original input signal thatgenerates a residue voltage.

Fig. 2. General Pipeline ADC Architecture [1]

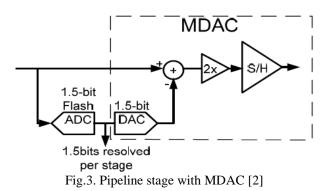

Fig.3. shows a common implementation of a pipeline ADC stage. Typically, the DAC, summer, gain stage and sample and hold are implemented together in one block called a multiplying digital-to-analog converter (MDAC).

The residue voltage is amplified and input into the next stage of the pipeline until the desired number of bits has been resolved.

International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

## II. 1.5 BITS/STAGE PIPELINE ADC

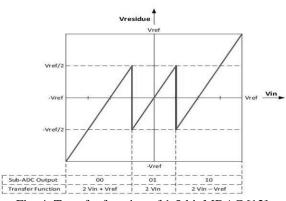

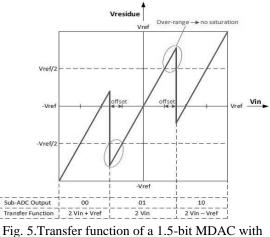

Fig.4. shows the transfer function of a 1.5-bit MDAC that The opamp is used in the MDAC for the gain stage. It's applies DEC. A 1.5-bit sub-ADC quantizes the input to 3levels and the residue is limited to half the full-scale range. gain is equal to the stage gain. The three opamp design If comparator threshold offsets forces the residue signal to fall outside normal range, the residue signal will be accurately passed into the next stage provided the offset is within  $\pm V_{ref}$  / 4 . Fig.5. demonstrates this by showing the transfer function of a 1.5-bit MDAC when there are threshold offsets in the sub-ADC. The fourth level is removed because the MDAC only needs to indicate whether the residue output is above or below  $V_{ref}$  / 2 and therefore, there is only an overlap of half bit. The accuracy of the 1.5-bit sub-ADC reduces from N bit to 2 bits using DEC. Generally, by using DEC, the accuracy of the sub-ADC can be increase if fewer bits are resolved in each stage.

Fig. 4. Transfer function of 1.5-bit MDAC [12]

The pipeline ADC applies DEC and consists of a front-end S/H, 8 pipeline stages, and a 2-bit flash ADC in last stage. Each pipeline stage resolves 1.5 bits/stage, which is represented by a 2 output lines of single bit. In the end, a total of 18-bits are generated from a single input sample. To apply DEC, the bits from each adjacent pipeline stage overlap by half a bit and form the expected 4-bit output.

comparator offset[12]

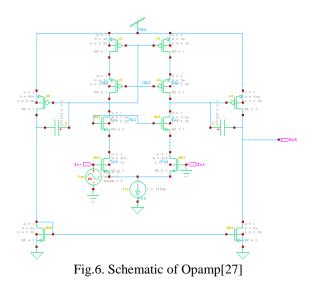

#### **III. OPAMP DESIGN**

configured in a closed-loop circuit where the closed-loop parameters that are discussed next are gain, bandwidth, and output swing [27].

The settling accuracy refers to how close the residue output settles to its intended value and therefore, it can limit the accuracy of the ADC. Assuming the opamp has sufficient time to settle to its final value, the opamp's open-loop gain, A, sets the settling accuracy. This is because a higher open-loop gain results in a more accurate stage gain and in turn, the residue output follows a more accurate transfer function. To ensure the residue settles to with  $\Delta LSB$ , the loop gain of the closed-loop,  $A\beta$ , must be:

$$A\beta > \frac{2^{N}}{\Delta}$$

Where  $\beta$  is the feedback factor of the closed-loop circuit

and  $1LSB = \frac{1}{2^{N}}$ . The loop gain, as the name suggests, is

the gain around the opamp closed-loop circuit.

Considering there are other sources of error (e.g. thermal noise), a reasonable choice is  $\Delta = 0.25 LSB$ . For

instance, the front-end sample and hold and first pipeline stage in a 4-bit pipeline ADC requires a loop gain of :

$$\frac{2^{10}}{0.25} = 4096$$

Assuming the opamp has sufficient gain to accurately settle to its final value, the opamp speed, which determines how fast the residue output settles to a final value, sets the settling accuracy. The bandwidth must be high enough for the opamp to settle to a sufficiently accurate value within

the required time of half a sampling period,  $0.5 / f_{e}$

## International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

opamp bias circuits are required to provide a cascode bias to each opamp. Bias voltages for cascade opamp are designed by using the wide-swing cascode current mirrors [3]. A small amount of current scaling is used in this design so as to provide a continuous power scaleable range. As such the bias circuit must keep M2 and M3 in Figure 4.2 in the active region regardless of the bias current (and thus level of channel inversion).

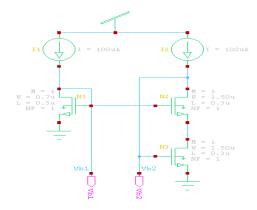

Fig.7. Bias circuit for Opamp[27]

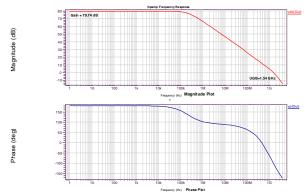

Opamp Gain and phase plot is shown in the Fig. 8.

Fig.8. (a) Gain Plot of Opamp (b) Phase Plot of Opa-amp

# **IV. SAMPLE AND HOLD**

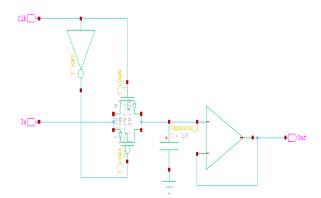

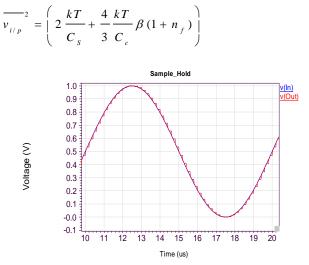

The Sample and Hold located at the front of the pipeline performs the first step of sampling the external input signal. Figure 4.7 shows the Sample and Hold circuit used in this ADC.  $\phi_1$  and  $\phi_2$  are the clock phase for sample and hold respectively. The total input sampling capacitance the external source must drive in  $\phi_1$  is  $C_{iT,S/H} = C_s \cdot \ln \phi_2$ , the sample and hold drives a load capacitance to hold the sampled voltage for the pipeline stage. The capacitance  $C_s$  does not load the opamp because it's top plate has no path ground. As a result, the feedback factor of the sample and hold is:

$$\beta_{S/H} = \frac{C_S}{C_S + 0} = 1$$

Fig.9. Sample and Hold Circuit[28]

However, the total input sampling capacitance of the sub-ADC,  $C_{iT,subADC}$ , and of the MDAC,  $C_{iT,MDAC}$ , in the next stage does load the sample and hold opamp. The opamp is also loaded by an additional capacitance,  $C_{n2}$ . The total output load on the sample and hold opamp is:

$C_{L,S/H} = C_{iT,subADC} + C_{iT,nextstageMDAC} + C_{n2}$

From [17], the differential input-referred thermal noise power of a sample and hold or an MDAC is:

Fig.10. Transient response of Sample and Hold circuit

Where  $C_c$  is the compensation capacitor used to stabilize the opamp closed-loop circuit. As the input signal is being sampled in  $\phi_1$ , thermal noise from the transistor is sampled across  $C_s$ .

The opamp is not used and therefore, does not contribute any noise. The dominate sourse of noise is from the Opamp's first stage, the noise from the second stage is negligible because, once input-referred, it is greatly reduced by the gain of the opamp. The noise fraction,  $n_{e}$

, defined in equation 4.12. The formula is based on a similar calculation performed on a simple opamp in [18].

## International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

$$n_f = \frac{g_{m3} + g_{m9}}{g_{m1}}$$

Since typically  $n_f = 1$  and  $\beta_{S/H} = 1$ , thus

the input referred thermal noise power of the S/H block is

$$\overline{v_{i/p,S/H}}^2 = \left(2\frac{kT}{C_s} + \frac{4}{3}\frac{kT}{C_c}\right)$$

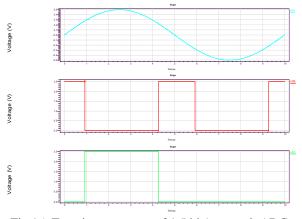

#### V. MDAC DESIGN

Since 1.5 bits/stage architecture has one of three digital outputs, thus the DAC has three operating modes.

ADC output=01: No over range error (stage input is

between

$$-\frac{V_{ref}}{4}$$

and  $+\frac{V_{ref}}{4}$  ).During  $\phi_1$

$Q_{c1} = C_1 V_{in} Q_{c2} = C_2 V_{in}$  During  $\phi_2$ : C<sub>1</sub> is discharged, thus by charge conservation:  $C_1 V_{in} + C_2 V_{in} = C_2 V_{out}$ (noting negative feedback forces node V<sub>p</sub> to a virtual

ground) Thus  $V_{out} = \frac{C_1 + C_2}{C_2} V_{in} \rightarrow if C_1 = C_2 then : V_{out} = 2V_{in}$

Fig.11. Multiplying Digital to analog converter [10]

ADC output=10: Over range error-Input exceeds  $+\frac{V_{ref}}{4}$ ,

thus subtract  $\frac{V_{ref}}{2}$  from input during  $\phi_1$ :  $Q_{C1} = C_1 V_{in}, Q_{C2} = C_2 V_{in}$

During  $\phi_2$ :  $C_1$  is charged to  $V_{ref}$ , thus by charge conservation  $C_1 V_{in} + C_2 V_{in} = C_1 V_{ref} + C_2 V_{out}$

$$\therefore V_{out} = \frac{C_1 + C_2}{C_2} V_{in} - \frac{C_1}{C_2} V_{ref} \rightarrow if, C_1 = C_2, then : V_{out} = 2V_{in} - V_{ref} = 2(V_{in} - V_{ref})$$

ADC output=00: Under range error-Input below –  $\frac{v_r}{d}$

add

$$\frac{V_{ref}}{2}$$

to input During  $\phi_1$  :

$Q_{C1} = C_1 V_{in}, Q_{C2} = C_2 V_{in}$  During  $\phi_2$ : C<sub>1</sub> is charged to  $-V_{ref}$ . Thus by charge conservation

$$C_{1}V_{in} + C_{2}V_{in} = C_{1}(-V_{ref}) + C_{2}V_{out}$$

.  $V_{out} = \frac{C_{1} + C_{2}}{C_{2}}V_{in} + \frac{C_{1}}{C_{2}}V_{ref} \rightarrow if, C_{1} = C_{2}, then: V_{out} = 2V_{in} + V_{ref} = 2(V_{in} + V_{ref} / 2)$

Thus the switched capacitor circuit can be used to implement the sample-and-hold, gain stage, DAC, and subtraction blocks of ADC. To reduce the signal dependent charge injection bottom plate sampling technique is where the use of an advanced clock  $\phi_{1p}$ , makes charge injection signal independent [10]. The total input sampling capacitance in  $\phi_1$  is  $C_{iT,MDAC} = C_1 \cdot \ln \phi_2$ , the two  $C_1 / 2$  capacitors apply a load of  $C_1 / 4$  on the MDAC opamp. Taking into consideration the loading effects of the next stage and of the parasitic capacitance  $C_{n2}$ , the total output load on the MDAC opamp is:

$$C_{L,flipMDAC} = C_1 / 4 + C_{iT,subADC} + C_{iT,nextstageMDAC} + C_{n2}$$

The feedback factor of MDAC is:

$$\beta_{_{MDAC}} = \frac{C_{_{1}}/2}{C_{_{1}}/2 + C_{_{1}}/2} = \frac{1}{2}$$

The differential input-referred noise of MDAC is:

$$\overline{v_{i/p,MDAC}}^{2} = \left(2\frac{kT}{C_{1}} + \frac{4}{3}\frac{kT}{C_{2}}\left(\frac{1}{2}\right)(2)\right)$$

Fig.12. transient response of MDAC for sinusoidal input at 300 kHz, 0.5 V

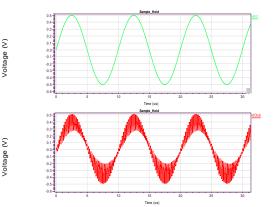

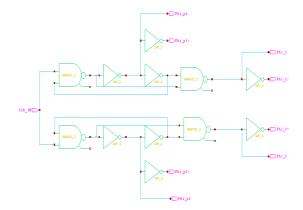

#### VI. NON OVERLAPPING CLOCK GENERATOR

Non-overlapping clocks are required in the MDAC to  $\binom{2}{2}$  minimize the effect of signal-dependent charge injection. Non-overlapping clocks were generated using the design of Figure 5.11, where the non-overlap time is given by the minimum delay of  $t_2$  and  $t_2+t_3+t_5$ .

# International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

Fig.13. Non-Overlapping Clock generator circuit [33]

For this design, to improve the likelihood of design functionality a longer non-overlap time has been favoured.

Fig.14. Non-Overlapping Clock

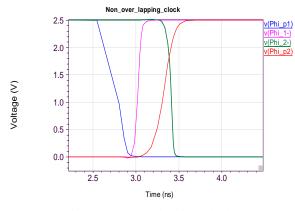

# **VII. COMPARATOR**

Comparator used in this paper consists of three stages: the input preamplifier, output buffer stage and decision stage. The preamplifier section improvise the sensitivity of comparator to input signal by amplifying the input signal, it also isolates from the switching noise emerging from the positive feedback. The positive feedback stage increases the gain and produces an output to decide which of the input signals is larger. The output buffer also provides some gain and couples it to the other digital circuits.

Schematic of pre-amplification stage is shown in Fig. 15; This circuit is differential amplifier with active loads. The sizes of M6 and M7 are set by considering the differential

amplifier trans-conductance,  $g_m$ , and input capacitance.

The trans-conductance of M1 and M2 decides the gain of the stage, while M6 and M7 determines the input capacitance of the comparator.

Transistor M9 and M8 are used as current mirror to bias the preamplifier stage at bias current of 12  $\mu$ A. transistor M1 and M4 are active load to the preamplifier stage. This is to ensure high speed. The relation between input

voltages and output current  $i_o$  is given by

Fig.15. Schematic of Comparator

The decision circuit is the important section of comparator that can discriminates mV level signals. The circuit used in the comparator is shown in Figure 4.4 which uses positive feedback from the cross-gate connection of M10 and M11 to increase the gain of the decision element.

In this circuit M9 and M12 are identical similarly M10 and M11 are identical. The output voltage of non-inverting terminal is given by

$$V_{op} = \sqrt{\frac{2i_{op}}{\beta_{9}}} + V_{THN}$$

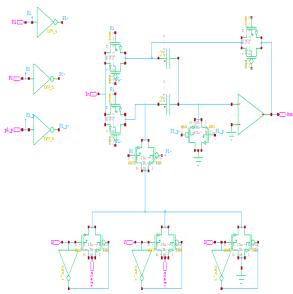

#### **VIII. FOUR BIT PIPELINE ADC**

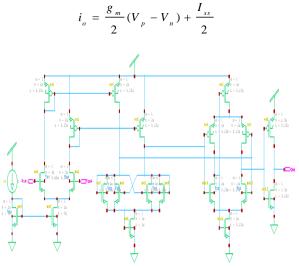

The complete schematic of 4-bit pipeline ADC is shown in figure 4.12, First and second stage are identical and sampled capacitor C2 =C1= 1  $\mu$ F is used. After second stage scaling is done to reduce the power consumption and uses C1=C2=0.5  $\mu$ F and 0.25  $\mu$ F for third, fourth stage respectively.

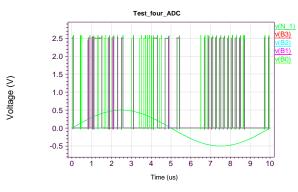

The setup of 4-bit pipeline ADC is shown in Fig.17, for a sinusoidal signal of 5 MHz. And the simulated 4 bit output is shown in the figure 5.9

Fig.16. Transient response of 1.5 bit/stage sub ADC

# International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

Fig.17 Transient response of 4-bit ADC

#### **IX. PERFORMANCE SUMMARY**

| Technology      | 0.25 µm CMOS process |

|-----------------|----------------------|

| Resolution      | 4 bit                |

| Supply Voltage  | 2.5 V                |

| Conversion rate | 5 MS/s               |

| Power           | 78.12mW              |

# X. CONCLUSION

The goal of this paper was to design a 2.5 V, 1.5 bit/stage 4bit ADC by using switched capacitor technique. The ADC is designed in 0.25  $\mu$ m CMOS process at 2.5 V supply voltage. It also shows the comparison between the power consumption of stages with the S/H and without S/H which gives 28.33 mW in first stage (with S/H) and 19.59 mW third stage (without S/H).Further the ADC is tested at input frequency of 1 MHz and sampling rate of 5 MS/s, at which ADC consumes 78.12mW power.

#### REFERENCES

- J. Yuan, S.W. Fung, "A 12-bit 20 MS/s 56.3 mW Pipelined ADC With Interpolation-Based Nonlinear Calibration", IEEE Transactions on circuits and systems, Regular paper, Vol. 59, No. 3, March 2012.

- [2] Y. Lin, K. Doris, "An 11b Pipeline ADC With Parallel-Sampling Technique for Converting Multi-Carrier Signals", IEEE Transactions on circuits and systems, Regular paper, Vol. 59, No. 5, May 2012.

- [3] N. Sun, "Exploiting Process Variation and Noise in Comparators to Calibrate Interstage Gain Nonlinearity in Pipelined ADCs", IEEE Transactions on circuits and systems, Regular paper, Vol. 59, No. 4, April 2012.

- [4] T. Miki, T. Morie, "An 11-b 300-MS/s Double-Sampling Pipelined ADC With On-Chip Digital Calibration for Memory Effects", IEEE Journal of solid state circuits, Vol. 47, No. 11, November 2012.

- [5] J. Kyung, R. Kim, "A 12-b, 30-MS/s, 2.95-mW Pipelined ADC Using Single-Stage Class-AB Amplifiers and Deterministic Background Calibration", IEEE Journal of solid state circuits, Vol. 47, No. 9, September 2012.

- [6] S. Lee, A.P. Chandrakasan, "A 12 b 5-to-50 MS/s 0.5-to-1 V Voltage Scalable Zero-Crossing Based Pipeline ADC", IEEE Journal of solid state circuits, Vol. 47, No. 7, July 2012.

- [7] C.y. Chen, J. Wu, "A 12-Bit 3 GS/s Pipeline ADC With 0.4 mm<sup>2</sup> and 500 mW in 40 nm Digital CMOS", IEEE Journal of solid state circuits, Vol. 47, No. 4, April 2012.

- [8] T. Sundstrom, C. Svensson, "A 2.4 GS/s, Single-Channel, 31.3 dB SNDR at Nyquist, Pipeline ADC in 65 nm CMOS", IEEE Journal of solid state circuits, Vol. 46, No. 7, July 2011.

- [9] J. Yuan, S.W. Fung, "An Interpolation-Based Calibration Architecture for Pipeline ADC With Nonlinear Error", IEEE Transactions on instrumentation and measurement, Vol.61, No.1, January 2012.

- [10] C.J. Tseng, H.W. Chen, "A 10-bit 320-MS/s Stage-Gain-Error Self-Calibration Pipeline ADC", IEEE Journal of solid state circuits, Vol. 47, No. 6, June 2012.

- [11] C.S Shin, G.C. Ahn, "A 10-bit 100-MS/s Dual-Channel Pipeline ADC Using Dynamic Memory Effect Cancellation technique", IEEE Transactions on circuit and system, Express Briefs, Vol. 58, No. 5, May 2011.

- [12] K. Chandrashekar, M. Corsi, "A 20-MS/s to 40-MS/s Reconfigurable Pipeline ADC Implemented With Parallel OTA Scaling", IEEE Transactions on circuits and systems, Express briefs, Vol. 57, No. 8, August 2010.

- [13] S. Devarajan, L. Singer, "A 16-bit, 125 MS/s, 385 mW, 78.7 dB SNR CMOS Pipeline ADC", IEEE Journal of solid state circuits, Vol. 44, No. 12, December 2009.

- [14] A. Verma, B. Razavi, "A 10-Bit 500-MS/s 55-mW CMOS ADC", IEEE Journal of solid state circuits, Vol. 44, No. 11, November 2009.

- [15] N. Sasidhar, Y.J. Kook, "A Low Power Pipeline ADC Using Capacitor and Opamp Sharing Technique With a Scheme to Cancel the Effect of Signal Dependent Kickback", IEEE Journal of solid state circuits, Vol. 44, No. 9, September 2009.

- [17] B.G.Lee, B.M.Min, "A 14-bit 100 MS/s Pipeline ADC with a Merged SHA and First MDAC", IEEE Journal of solid state circuits, Vol.24, No. 12, December 2008.

- [18] K. Honda, M. Furuta, "A Low-Power Low-Voltage 10-bit 100-MSample/s Pipeline A/D Converter Using Capacitance Coupling Techniques", .IEEE Journal of solid state circuits, Vol.24, No. 4, December 2007.

- [19] S.T. Ryu, B.S. Song, "A 10-bit 50-MS/s Pipeline ADC WithOpamp Current Reuse", IEEE Journal of solid state circuits, Vol.42, No. 3, March 2007.

- [20] D. Kurose, T. Ito, "55-mW 200-MSPS 10-bit Pipeline ADCs for Wireless Receivers", IEEE Journal of solid state circuits, Vol.41, No. 7, July 2006.

- [21] I. Ahmed, "Pipeline ADC Design and Enhancement Techniques", Springer publication-2010, Ch-3, pp-19-36.

- [22] M.J.M. Pelgrom, "Analog-to-Digital Conversion", Springer publication- 2010, Ch 7,8, pp-203-318.

- [23] M. Gustavsson, J.J Wikner, and N.N Tan, "CMOS Data Converters for Communication", Kluwer Academic Publishers-2002, Ch-1,5, pp-1-25 and 125-137.

- [24] R.V.D. Plassche, "CMOS Integrated Analog-to-Digital and Digitalto-Analog Converters", Kluwer Academic Publishers-Second Edition, Ch-13, pp-523-549.

- [25] J.R. Amaya, M.D. Restituto, A.R. Vazquez, "Device-Level Modeling and Synthesis of High-Performance Pipeline ADCs", Springer-2011, Ch-1,2, pp-1-25 and 29-34.

- [26] J. Baker, "CMOS Circuit Design, Layout, and Simulation", Wiley Indian Edition second Edition, Ch-27, pp-909-928.

- [27] M.J. Demler , "HighispeedAnalog-to-Digital Conversion", Academic Press, Inc.-1991, Ch-1, pp-1-19,

- [28] B. Razavi, "Principal of Data Conversion System Design", IEEE Press Circuit and System society, Ch-6, pp-96-147.

- [29] G. Zhang, "A Low-Power Pipeline ADC with Front-End Capacitor Sharing", Master of Applied Science thesis University of Toronto, Ch-3, pp-17-26.

- [30] http://www.maximintegrated.com/app-notes/index.mvp/id/283.

- [31] P.E. Allen, D.R. Holberg, "CMOS Analog Circuit Design", International student edition oxford university press-2010, Ch-8,9, pp-439-483 and 492-561.

- [32] B. Razavi, "Design of Analog CMOS Integrated Circuits", Tata McGraw-Hill Edition-2002, Ch-9, pp-291-336.